# DESIGN & ANALYSIS OF 4-BIT COUNTER USING SUB-MICRON TECHNOLOGY

Ms.ManishaRahamatkar, Ms. MittalPisalkar, Mr. YogeshThakare

Abstract:- This project is aim to design a 4-bit asynchronous counter using D flip flop. A counter is a collection of flip flop each representing a digit in a binary number representation.Counting is a fundamental function of digital circuits. A digital counter consists of a collection of flip-flops that change state (set or reset) in a prescribed sequence. Asynchronous counter is also known as serial or ripple counter. The name asynchronous comes from the fact that this counters flipflop are not being clocked at the same time. The clock input is applied only to the first flip flop. D flip flops are the basic memory element which is used in many of the applications with this proposed and existing flip flop an asynchronous counter was designed.Power comparison was made between the counters where the asynchronous counter designed using proposed flip flop gives low power consumption when compared to the existing one. We are designing 4-bit counter using different types of VLSI tools.VLSI is very large scale integrated circuit it is the process of creating an integrated circuit by combining thousands of transistors into a single chip.Power dissipation is one of the most important factors in VLSI circuit design it also maximize the speed and reduces area of the circuit to reduce the cost of the device There are different types of VLSI tools such as Tanner, DSCH and Microwind tool,VLSIcad,etc.We are using Microwind tool.

Keyword :- Counter , flip flop , asynchronous , VLSI .

# I. INTRODUCTION

Counters are sequential circuits that keep tract of the number of pulses applied on their inputs. Counters are one of the many applications of sequential logic that has a widespread use from simple digital alarm clocks to computer memory pointers.A counter is a collection of flipflops, each representing a digit in a binary number representation. We are designing a 4-bit counter by using a D flip- flop.It is a storage element based on gated latch principle, which can have its output changed only on the edge of the controlling clock signal.D flip flop is constructed by connecting NOT gate between two terminals of J-K flip flop.D flip flop is delayed flip flop where input is transfer to output with delay. The D flip flop also means differential amplifier. The work manner is same for the JK flip flop only difference is the D flip flop are used in the NOT gate. The area and power conception will be reduced so the D flip-flop is used. The particular counter we have choosen for design is asynchronous counter with serialcarry output and input reset options .With the serial carry output it is possible for it to be cascaded to build a counter

with more bits and the input reset pin enables the user to set the counter to 'all-zero' state and then to start it counting again from the beginning, when it is desired. The objective of this project is to design the asynchronous circuit and analyze the different characteristics such as power consumption, efficiency and area occupation etc. designed using microwind .The design of a 4-bit Counter has allowed us to implement the various digital VLSI concepts learnt in the course to put to practical use and experience a very powerful VLSI modelling tool. This work Describes the different steps of the VLSI design, performance measurement of a 4-bit simulation and counter . VLSI is a very large integrated circuit this is the field which involves packing more and more logic devices into smaller and smaller areas. VLSI (very large-scale integration) is the current level of computer microchip miniaturization and refers to microchips containing in the hundreds of thousands of transistor . Logic circuits are widely used in modern low power VLSI circuits. This work describes the different steps of the VLSI design, simulation and performance measurement of a 4-bit counter. By performing simulations in different types of VLSI tools, it is possible to understand the effect of the varying the transistor sizes to obtain the desired output parameters There are different types of VLSI tools out of which we are using MICROWIND tool. The MICROWIND program allows us to design and simulate an integrated circuit at physical description level. The package contains a library of common logic and analog ICs to view and simulate. MICROWIND includes all the commands for a mask editor as well as original tools never gathered before in a single module . MICROWIND is a tool for designing and simulating circuits at layout level. The tool features full editing facilities ( cut , copy , move , duplicate , past ) various views MOS characteristics,2D cross section ,3D process viewer, and an analog simulator.

# II. PRIOR WORK

During the mid-1920s, several inventors attempted devices that were intended to control current in solid-state diodesand convert them into triodes, germanium crystals for use as radar detectors led to improvements in fabrication and in the understanding of quantum mechanical states of carriers in semiconductors. Then scientists who had been diverted to radar development returned to solid-state device development. With the invention of transistors at Bell Labs in 1947, the field of electronics shifted from vacuum tubes to solid-state devices. With the small transistor at their hands, electrical engineers of the 1950s saw the possibilities of One problem was the size of the circuit. A complex circuit, like a computer, was dependent on speed. If the components of the computer were too large or the wires interconnecting them too long, the electric signals couldn't travel fast enough through the circuit, thus making the computer too slow to be effective. Jack Kilby at Texas Instruments found a solution to this problem in 1958. Kilby's idea was to make all the components and the chip out of the same block (monolith) of semiconductor material. Kilby presented his idea to his superiors, and was allowed to build a test version of his circuit ready. Although the first integrated circuit was crude and had some problems, the idea was ground breaking. By

and had some problems, the idea was ground breaking. By making all the parts out of the same block of material and adding the metal needed to connect them as a layer on top of it, there was no need for discrete components. No more wires and components had to be assembled manually. The circuits could be made smaller, and the manufacturing process could be automated. From here, the idea of integrating all components on a single silicon wafer came into existence, which led to development in small-scale integration (SSI) in the early 1960s, medium-scale integration (MSI) in the late 1960s, and then large-scale integration (LSI) as well as VLSI in the 1970s and 1980s, with tens of thousands of transistors on a single chip (later hundreds of thousands, then millions, and now in billions).

# III. PROPOSED SYSTEM

The counter is a special case of the sequential circuits. Its function is to count the input pulses (clock signal) and store the result till the arrival of the next signal. The counting process therefore consist of a series of storage and addition operations. The counters are built from flip-flops and of gate circuits. There are two types of counter they are as follows :-

3.1 Asynchronous Counter :-

The clock circuit in which the clock pulses to be count are applied to only one flip-flop and other flip-flop are driven by the output of previous flip-flop , is known as asynchronous counter . It is also called as ripple counter. 3.2 Synchronous counter :-

The counter circuits , in which the clock pulses are simultaneously applied to all flip-flops , are known as synchronous counter .

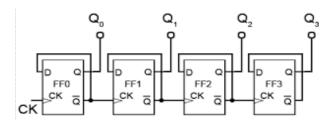

**Fig. Block diagram of 4 bit asynchronous counter** Above figure shows the diagram of asynchronous 4-bit counter using D flip-flop.

It is shown in the figure that clock pulse is given to only first flip flop and other flip-flop are clocked by output of previous flip-flop. The modified form of clocked SR flipflop and JK flip flop is a d flip-flop. The letter D stands for delay and such flip-flop are used for storing information . It is obtained by connecting a NOT gate between SR flipflop or J and K terminal in the JK flip-flop. The transfer of data from input to output is delayed and hence, it is called as Delay (D) flip-flop . As the name implies the purpose of a D FF is to temporary store (or delay) a single bit. A signal of 0 or 1 present at the input D is transferred to the output Q whenever the clock CLK is set to 1. When the clock triggers, the value remembered by the flip-flop becomes the value of the D input (Data) at that instant. One of the main disadvantages of the basic SR NAND Gate bistable circuit is that the indeterminate input condition of "SET" = logic "0" and "RESET" = logic "0" is forbidden. This state will force both outputs to be at logic "1", over-riding the feedback latching action and whichever input goes to logic level "1" first will lose control, while the other input still at logic "0" controls the resulting state of the latch. But in order to prevent this from happening an inverter can be connected between the "SET" and the "RESET" inputs to produce another type of flip flop circuit known as a Data Latch, Delay flip flop, D-type bistable, D-type Flip Flop or just simply a D Flip Flop as it is more generally called .

# **IV. METHODOLOGY**

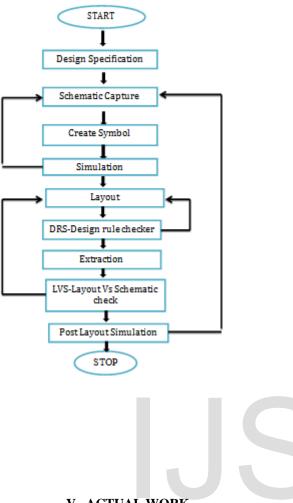

We are designed for 4 bit counter and results are evaluated for parameters like area, delay, speed and power . This work can be further extended for higher number of bits. New architectures can be designed in order to reduce the power , area and delay of the circuits . Steps may be taken to optimize the other parameters like frequency, number of gate clocks, length etc. In this work,we propose asynchronous circuit for a 4 bit binary counter using microwind. The propose asynchronous circuit is the first attempt of designing the mentioned counter. It has minimum complexity and quantum cost considerably and efficient design in terms of hardware complexity, constant inputs, garbage outputs and number of gates . More complex systems can be also developed using our proposed approach . Flow chart is shown below :-

#### V. ACTUAL WORK

Very-large-scale integration (VLSI) is the process of creating an integrated circuit (IC) by combining thousands of transistors into a single chip. LSI is large scale integration means microchips containing thousands of transistors . VLSI began in the 1970s when complex semiconductor and communication technologies were being developed. The microprocessor is a VLSI device. Before the introduction of VLSI technology most ICs had a limited set of functions they could perform. VLSI circuits are everywhere in computer, car, brand new state-of-the-art digital camera, the cell-phones . This is the field which involves packing more and more logic devices into smaller and smaller areas. The design of a 4-bit Counter has allowed us to implement the various digital circuit. Power dissipation is one of the most important factor of VLSI design. VLSI concepts learnt in the course to put to practical use and experience a very powerful VLSI modelling tool. This work describes the different steps of the VLSI design, simulation andperformance measurement of a 4-bit counter. VLSI (very large-scale integration) is the current level of computer microchip miniaturizationand refers to microchips containing in the hundreds of thousands of transistor. There are different types of VLSI tools out of which we are using MICROWIND tool. The MICROWIND program allows us to design and simulate an integrated circuit at physical description level. The simulation output can be observed as a waveform after the application of the input. The package contains a library of common logic and analog ICs to view and simulate .MICROWIND includes all the commands for a mask editor as well as original tools never gathered before in a single module . MICROWIND is a tool for designing and simulating circuits at layout level. The tool features full editing facilities ( cut , copy , move , duplicate , past ) various views MOS characteristics,2D cross section ,3D process viewer , and an analog simulator .

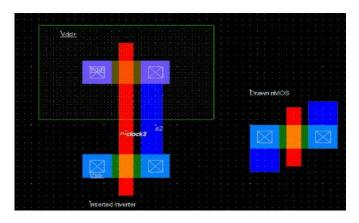

Fig.5.1 Design of NOT GATE in Microwind tool

The above figure shows the design of NOT GATE using PMOS and NMOS in microwindtool . PMOS having mesh loop , the GATE terminal of PMOS is connected to the GATE terminal of NMOS by using polysilicon where clock pulse is applied . The source terminal of PMOS is connected to the drain terminal of NMOS by using polysilicon .Vdd supply is given to the drain terminal of PMOS and to the mesh loop of PMOS and source terminal of NMOS is grounded . Finally in design rule checker the design of the circuit is verified and then we select the run option to observe the output . In this way design is verified and andout put is observed in microwindtool .

# Fig. 5.2 Output of NOT GATE observed in Microwind tool

The above waveforms shows the output of NOT GATE. It is observed from the waveform that where logic '0' is given in output it is inverting to logic '1'. The NOT gate is an electronic circuit that performs negation. Therefore, NOT GATE is also known as an invertor. NOT GATE does take its operand and negate it that means it inverts the given input which is shown in the above result of NOT GATE. Hence, the design of NOT GATE is verified.

### V. CONCLUSION

This project will give us an opportunity to exercise our skills in designing (both schematics and layouts) digital VLSI circuits with the help of the state-of-the-art Custom IC Design Tools. From the different design steps we will learn about digital circuit design technique, proper choice of transistor sizes, design rules, laying out the circuit with minimum possible area, pre and post layout simulation (with Spectre), layout extraction, LVS matching and measurement of different performance factors. This work forms an important move in building large and complex sequential circuits so as to reduce the power consumption and improve application in low power and nanotechnology. This 4 bit asynchronous counter is best implemented using the 0.12micron technology is preferable over .6 micron technologies in maintaining the logic density in fabrication process, power optimization, reducing the propagation delay& surface area. Thus this counter implemented in CMOS.It will observe that the propose circuits have offered an improved performance in power dissipation, charge leakage and clock skew with additional burden of silicon area. The design of a 4-bit counter will allowed us to implement the various digital VLSI concepts learnt in the course to put to practical use and experience a very powerful VLSI modeling tool. It is also useful to get know-how of the various design rules learnt and how they should be avoided to ensure a good working design with minimum capacitances and occupying the minimum chip area.

#### REFERENCE

1] B.A.Gavhane and P. V. Kathole, Nanometric "4-Bit Binary Counter" with Parallel Load Using Reversible Logic, International Journal of Advanced Computer Engineering and Communication Technology (IJACECT), Volume -3, Issue -1, 2014.

2] A. Jamal and J. P. Prasad, "Design of Low Power Counters Using Reversible Logic", International Journal of Innovative Research in Science, Engineering and Technology, Vol. 3, Issue 5, May 2014.

3] K.Miranji, V.SuryaNarayana, and N.Syam Kumar, "Power Efficient Design of 4 Bit Asynchronous Up Counter Using D Flip Flop", International Journal of electronics & communication technology, IJECT Vol. 5, Issue spl - 3, Jan - March 2014.

4] Suresh Kumar.R P, "Power and Area Efficient Design of Counter for Low Power VLSI System", IJCSMC, Vol. 2, Issue. 6, June 2013.

5]VijayaBhaskarM,SuparshyaBabuSukhavasi,SusruthaBab uSukhavasi,GSanthiSwaroopVemana, "Implementation of Synchronous Up Counter by using Self Resetting Logic",International Journal of Engineering Research and Applications (IJERA),Vol. 2, Issue 1,Jan-Feb 2012, pp.972-981.

6] S Hirkaney, S Nemade, V Gupta, "Power Efficient Design of Counter on .12 Micron Technology", International Journal of Soft Computing and Engineering (IJSCE), Volume-1, Issue-1, March 2011.